在 2024 年 12 月举行的 IEDM 上股市加杠杆,台积电展示了:“2nm 平台技术,具有节能纳米片晶体管和互连,并与 3DIC 共同优化,适用于 AI、HPC 和移动 SoC 应用”。

在这篇评论中,我们将采用论文中的一些实质性细节以及我们自己的分析,并展示该工艺与竞争对手的 2nm 级工艺的比较。

在超范围的功率、性能和面积 (PPA) 方面,该论文指出,与之前的 3nm 节点相比,该工艺的功率提高了 30%,性能提高了 15%,密度提高了 1.15 倍以上。注意:3nm 论文参考表明这是与 N3E 而不是 N3 进行比较。

在 14nm(三星)/16nm(台积电)节点,三星和台积电均生产了 Apple A9 处理器。Tom 的硬件测量发现,三星版本的功率性能略优于台积电。我们认为 A9 首先是为三星设计的,因此这可能只是反映了一种针对三星进行了更优化的设计,然后移植到了台积电,尽管如此,两者之间的功率非常接近。从 14nm/16nm,到 10nm、7nm、5nm、3nm,现在到 2nm,三星和台积电都为每个节点提供了与前一个节点相比的相对功率改进。

在 10nm 工艺中,台积电比三星实现了更大的功率降低,并一直保持领先,直到 3nm 工艺时,三星的全栅极 (GAA) 提供了足够大的改进,基本缩小了与台积电 3nm FinFET 工艺在功率方面的差距(与 FinFET 相比,GAA 有望提供更大的功率改进)。

台积电2nm宣布相对于3nm,功率提升30%,大于三星25%的提升,台积电再次保持领先。

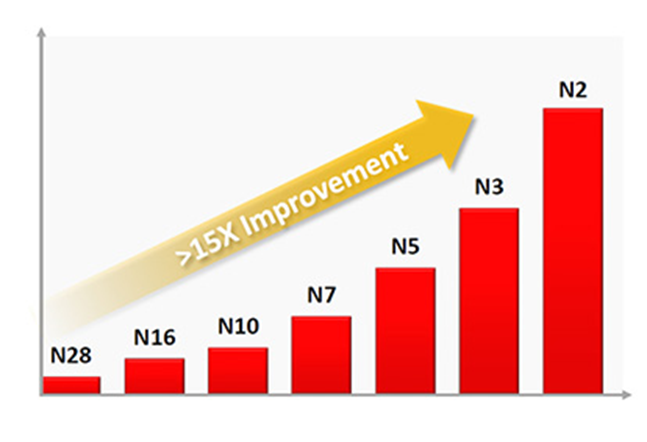

在论文展示过程中,展示了节点与功率效率和每瓦性能的图表。功率效率图表出现在论文的一个版本中,尽管它不是在会议论文集中发表的论文的“最终”版本中。幸运的是,我们捕捉到了功率效率图表,因为它非常有趣,值得分析,见图 1。

我们获取了图表图像,将其拉入 Excel 并创建一个 Excel 图表,将 28nm 条形图标准化为 1,然后输入其他条形图的值,直到它们与图表匹配。如果我们随后构建一组从 28nm = 1 开始的条形图,并根据台积电宣布的节点间功率改进进行放大,我们会得到不到 9 倍的总改进。从 N28 到 N10 的节点匹配良好,但从 N7 开始,图表上的条形图显示每个节点的改进比台积电宣布的要多。仅图表上的 N3 到 N2 条形图就显示了 55% 的改进,而宣布的改进为 30%。

目前尚不清楚是什么导致了这种差异,但这是一个很大的差距。这可能是为什么图表从最终论文中删除的原因。

与上面的功率分析类似,在三星 14nm/台积电 16nm 工艺上,Apple A9 处理器在两种工艺上的性能相同。将两种工艺标准化为 1,并应用两家公司公布的节点间性能改进,可以比较每个节点的性能。还可以使用英特尔 10SF 与台积电 7nm 工艺上的 AMD 处理器,将英特尔添加到分析中,并根据英特尔节点性能公告进行前向计算。

根据此分析,我们认为英特尔 18A 在 2nm 级工艺中性能最高,台积电位居第二,三星位居第三。

PPA 的第三部分是面积。我们分析了两个与“面积”相关的因素,一是高密度逻辑单元晶体管密度,二是 SRAM 单元大小。TechInsights 对台积电 N3E 工艺进行了详细的逆向工程工作,我们拥有计算标准高密度逻辑单元晶体管密度所需的所有间距。同样,我们也分析了三星 SF3E 和 SF3。本文中的台积电和三星的公开声明都提供了 2nm 的密度改进值。对于英特尔,我们在保密协议下拥有 18A 的所有间距,虽然我们不能透露具体间距,但我们可以进行密度比较。对于高密度逻辑单元,台积电在密度上远远领先于三星和英特尔,英特尔位居第二,三星位居第三。

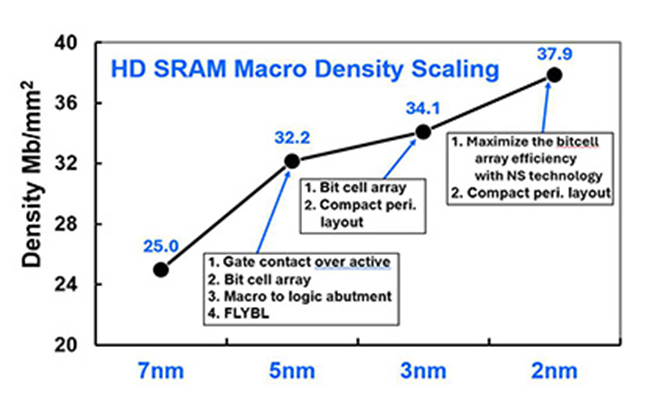

如前所述,台积电的论文不包括 SRAM 单元大小,但有一个 SRAM 密度与节点的图表,见图 3。

问题在于,SRAM 阵列不仅包括 SRAM 单元,还包括开销,例如 7nm 有 25.0 Mb/mm 2,7nm 的 SRAM 单元大小为 0.0270um 2。如果将 25.0Mb 乘以 SRAM 单元大小,则得到 0.675mm 2 。1.000 和 0.675mm 2之间的差异是开销,并且它在各个节点之间并不是恒定的,请参见表 1。

良率是当今的热门话题,很多报道称三星在 3nm 良率方面遇到困难并因良率低而失去客户,最近也有报道称英特尔 18A 的良率仅为 10%。

在该论文中,台积电报告称,256Mb SRAM 阵列的平均良率 >80%,峰值良率 >90%。目前开发阶段的这些良率表明缺陷密度极佳。除了在 SRAM 阵列中测试的良率成分外,还有其他良率成分,但这些结果令人印象深刻。

关于英特尔 10% 良率的报告,我们有两个独立的可靠来源告诉我们这根本不是真的,良率要比这好得多。关于 10% 良率报告的其他问题是芯片有多大/是什么,以及在开发的哪个阶段看到了这个良率,如果它是真的的话。根据我们的消息来源,我们认为报告的 10% 良率要么是错误的,要么是旧数据。

另一个被广泛流传的数字是,台积电2nm工艺的每片晶圆售价将达到3万美元。

TechInsights 提供全球领先的半导体成本和价格模型。在 3nm 投入生产之前,我们预计每片晶圆的成本低于 20,000 美元,一些客户联系我们,坚称 3nm 的价格为每片晶圆 20,000 至 25,000 美元。3nm 投入生产后,我们能够对台积电的财务状况进行专有取证,并确定我们是正确的,批量价格低于每片晶圆 20,000 美元,差数千美元。

从 3nm 晶圆每片不到 20,000 美元的价格到 2nm 晶圆每片 30,000 美元的价格,意味着价格上涨了 1.5 倍以上,密度也提高了 1.15 倍,晶体管成本大幅增加,这引发了一个问题:谁会支付这笔费用?我们的价格估计是每片不到 30,000 美元。还有报道称,苹果通常是台积电每个节点的主要客户,可能会因为价格原因放弃最初的 2nm 使用,尽管我们也听到了反对的声音。

此次讨论的另一个要素是,台积电的大批量晶圆价格比小批量晶圆价格低很多,因此在任何讨论中都需要考虑批量。总体而言,我们认为 30,000 美元高于平均到大批量的定价。

如果台积电 2nm 晶圆的价格为每片 30,000 美元,他们将给客户带来很大压力,迫使他们转向英特尔和三星获取 2nm 级晶圆供应。

台积电的论文没有涉及背面电力输送,但竞争对手的 2nm 工艺将实现背面电力输送。

英特尔 18A 将具有背面供电功能——英特尔将于 2025 年率先实现该技术。2026 年,三星 SF2P 工艺也将实现背面供电。最后,台积电预计根本不会在其 2nm 工艺变体上实现背面供电,而要等到 2027 年(最近的报道显示这一时间被推迟到 2026 年)才会在其 A16 工艺上实现。A16 背面供电预计将是直接背面连接,可以提供比英特尔和三星实现的更小的轨道高度。

由于英特尔是这三家公司中最注重性能的,因此他们首先实施背面供电是合情合理的。

我们听到的有关背面供电的另一件有趣的事情是,代工厂 HPC 客户想要它,但移动客户由于成本原因而不要。

对于多个节点,我们可能会看到有和没有背面供电的节点,考虑到它对金属 0 的影响,设计规则可能会有所不同。除此之外,为了获得最高性能,我们预计首先在通孔中引入钼,然后在关键互连中引入钼。这可能导致节点在 HPC 的背面供电和钼金属化之间分裂,而在移动设备的背面供电和铜金属化之间分裂。

论文中最后一个有趣的内容是关于“平面钝化”的评论。许多工艺都有顶部铝金属层,钝化遵循金属轮廓,如果需要混合键合之类的东西,晶圆表面必须是平坦的。平面钝化大概是平坦化的顶层,以便实现键合。

台积电已披露了一项 2nm 工艺,该工艺很可能是目前密度最高的 2nm 级工艺。至少与三星相比,它似乎也是最节能的。在性能方面,我们认为英特尔 18A 处于领先地位。早期的产量报告看起来很有希望,但我们认为 30,000 美元/片晶圆的定价报告并不代表该工艺的可接受价值,这可能为英特尔和三星提供抢占市场份额的机会。台积电 2nm 应该会在今年下半年投入生产。

参考链接

https://semiwiki.com/semiconductor-services/techinsights/352972-iedm-2025-tsmc-2nm-process-disclosure-how-does-it-measure-up/股市加杠杆